What is VHDL?

VHDL is a Hardware Description Language (HDL) codified in IEEE Standard 1076 and is used for designing logic to be implemented in FPGA and ASIC devices.

So, what is VHDL? VHDL allows the behavior of a system to be described/modeled for simulation, as well as describing circuits that can be synthesized into real hardware. Describing hardware requires the ability to describe concurrent processes. Concurrency means that different processes are executed simultaneously. This is the biggest difference between Hardware Description Languages and software languages. While software can imitate simultaneous processing of two different threads by quickly alternating between them, HDL describes circuits that will execute truly simultaneously.

History of VHDL

The Department of Defense created VHDL in the 1980s based on the Ada software language, with help from commercial entities. VHDL was originally an acronym for VHSIC Hardware Description language, with VHSIC meaning Very High-Speed Integrated Circuits. So, an acronym within an acronym – VHDL clearly grew out of the defense industry!

Basics of VHDL

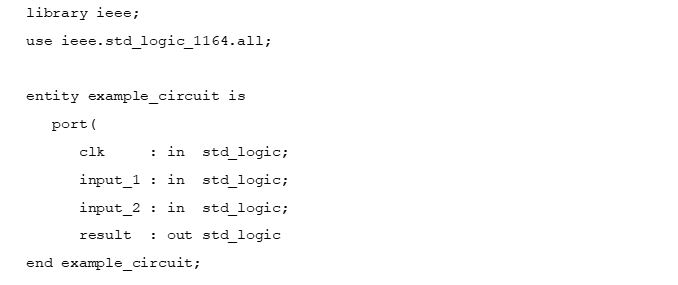

Entity Statement

The first step in designing a digital circuit is to define the boundaries of the box – the inputs and outputs. With VHDL, this is accomplished with an `entity` statement:

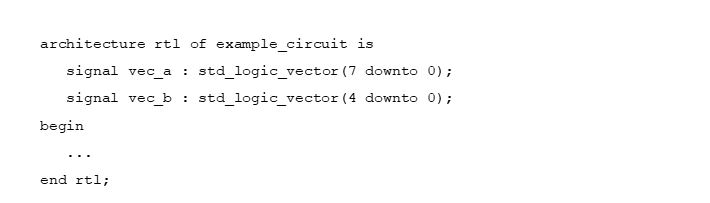

Architecture Statement

The next step is to define what is going on inside the box. In VHDL, this is done with an `architecture` statement:

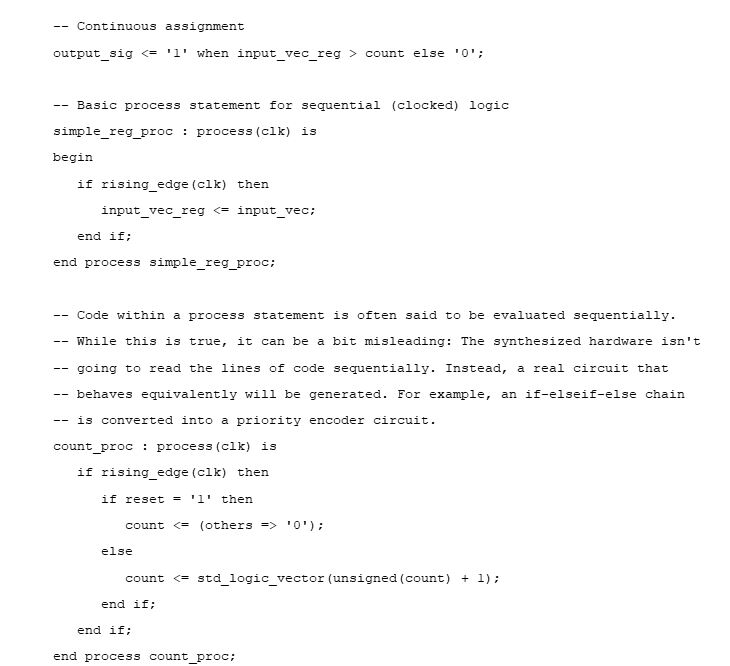

In the architecture section, designers add continuous assignment statements and process blocks. This is where HDL starts to behave significantly differently than software languages. Instead of following the code from top to bottom, each process and continuous assignment needs to be interpreted in parallel.

Strongly Typed Language

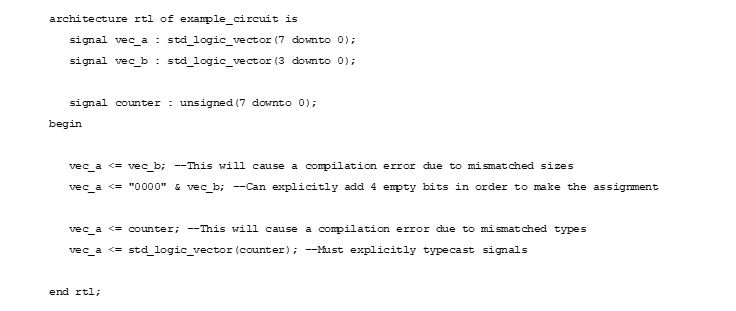

One of the hallmarks of VHDL is that it is a strongly typed language. This means that the compiler will complain anytime an operation is performed with mixed types, or sizes don’t exactly match. There aren’t any rules built into the language for the compiler to try to infer what the user intended. For example, VHDL won’t truncate extra bits on the left when assigning vectors of different lengths or automatically convert between `std_logic_vector` and `unsigned` types. VHDL requires that the code be explicit.

Some might call the language pedantic because of this, others will appreciate that VHDL compilers will report an error, rather than quietly assume the designer’s intent and cause errors during runtime that can be more difficult to identify.

VHDL Libraries

There is very little that is built into the VHDL language itself, so little in fact that it is left up to a few standard library packages to define even the most basic building blocks of a circuit design such a single bit type (`std_logic`) or a collection of bits (`std_logic_vector`). IEEE standardized several library packages that must be included in virtually all VHDL source files.

Standard Libraries

- ieee.std_logic_1164

- Defines the basic signal types such as `std_logic`, `std_ulogic`, and their array/vector versions `std_logic_vector` and `std_ulogic_vector`, and the various operators and conversion functions used with those types

- ieee.numeric_std

- Defines `unsigned` and `signed` vector types, as well as their operators and conversion functions

- ieee.math_real

- Defines the `rea`l type (a non-synthesizable floating-point format) as well as various math functions

- Only for non-synthesizable code and calculations that resolve at compile time (i.e., calculating the value of a generic or constant).

Non-Standard Libraries

- std_logic_arith

- std_logic_signed

- std_logic_unsigned

- std_logic_misc

IEEE deprecated the first three, so do not use them. Instead, the numeric_std package covers the same functionality. The std_logic_misc package is non-standard, but does not have a standard replacement. Users can run into trouble if they use non-standard packages, so it is best to stick with the IEEE approved packages.

Versions of VHDL

Various versions of the VHDL standard denoted with the year of release:

- IEEE Std 1076-2019

- IEEE Std 1076-2008

-

- Contains a lot of popular improvements, but not widely supported by tools

- IEEE Std 1076-2002

- IEEE Std 1076-2000

- IEEE Std 1076-1993

-

- The best bet for widespread tool support

- IEEE Std 1076-1987

Unfortunately, tool vendors have been very slow to adopt newer standards of the language. VHDL-2008 support grew over the years, but even as of Vivado 2023.2, it only supports a subset of the 2008 standard. The Vivado Design Suite User Guide on Synthesis (UG901) details which features AMD Vivado supports from the newer versions of VHDL. Support varies among other vendors and simulation tools as well. For that reason, VHDL-93 is still often used as the de facto standard. Users should double check what features are, and are not, supported by the tools they use.

Comparison of VHDL to Verilog / SystemVerilog

Unlike Verilog, VHDL doesn’t make any assumptions or guesses when it comes to designer intent. If a statement is ambiguous, it fails at compile time. This can be annoying for many engineers used to Verilog but can also be a benefit – the strong typing in VHDL doesn’t give users any extra rope with which to get themselves into trouble, whereas Verilog can allow bugs to silently enter the design.

Because of this, an argument can be made that VHDL could improve quality and reliability of synthesizable code. However, SystemVerilog is often preferred for simulations due to it additional features and flexibility.

VHDL seems to be more popular with defense/military contractors and on the East coast of the USA, whereas SystemVerilog seems to be more popular in commercial sectors and on the West coast.

Read a comparison of Verilog to VHDL.

Conclusion

At the end of the day, there isn’t a huge difference between HDL options when describing synthesizable code. Either language can describe any hardware that the other can, and users that understand the hardware they want to implement won’t have a hard time picking up the other language or converting between the two. The key is understanding the hardware first – then an internet search engine can always get users the syntax they need to make it happen in whatever their chosen language is.

Additional Resources:

Looking to learn more about VHDL? Try our Designing with VHDL course or check out our webinars on various topics.