In electronics and digital design with FPGAs and SoCs, the demand for more efficient, powerful, and faster hardware is unrelenting. Engineers and developers require ways to optimize their designs, making them faster and more energy efficient. One of the transformative technologies available to address this challenge is High-Level Synthesis (HLS). It plays a crucial role in bridging the gap between software and hardware, allowing designers to work at higher abstraction levels while still reaping the benefits of hardware acceleration.

What Is High-Level Synthesis?

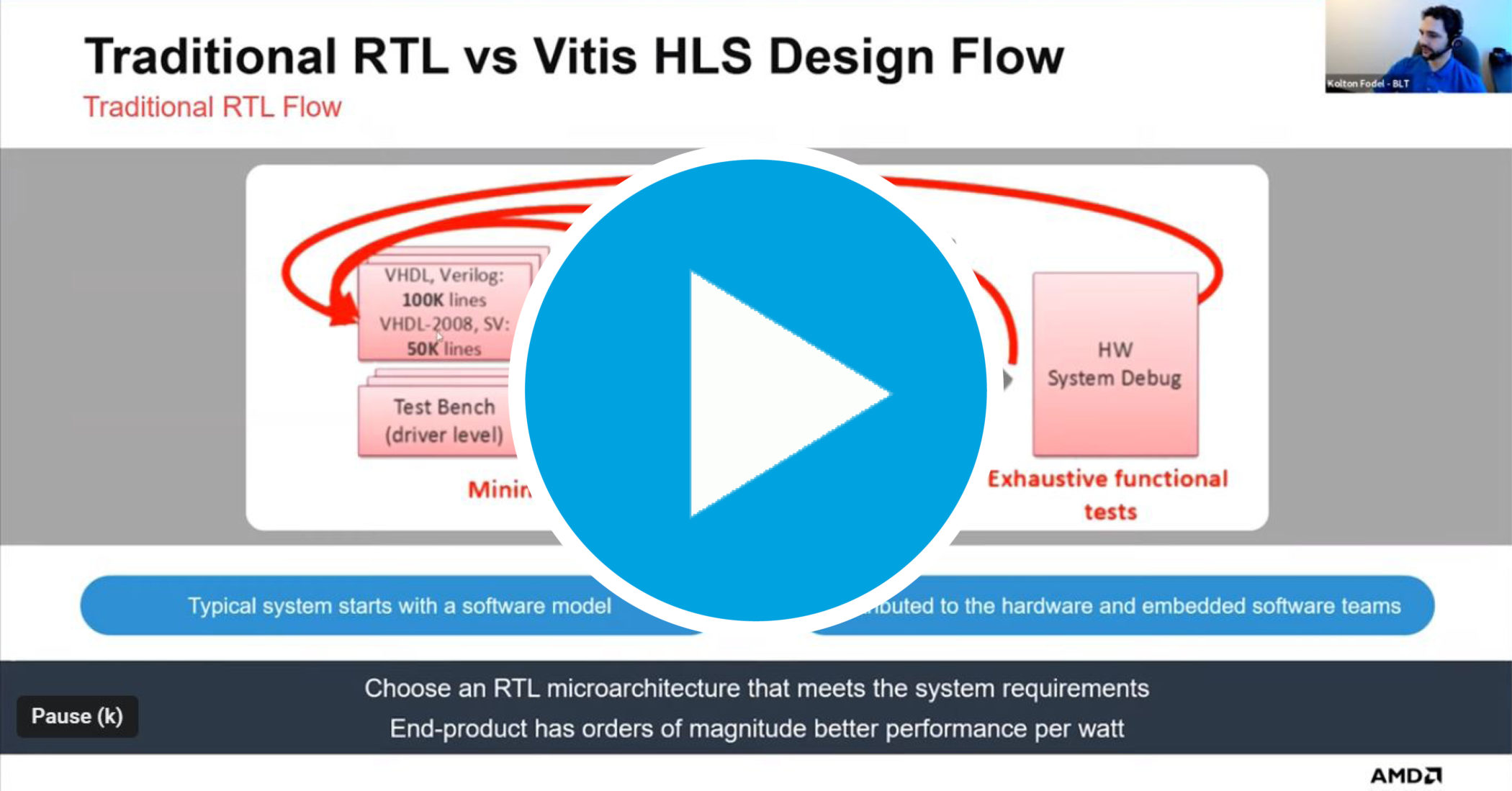

High-Level Synthesis is a design automation process that aims to simplify and accelerate the development of digital hardware. It transforms programming languages, such as C, C++, or SystemC, into hardware descriptions, usually in hardware description languages (HDLs) like Verilog or VHDL. Traditional hardware design methodologies require engineers to work with low-level HDLs directly. This can be time-consuming, error-prone, and require a deep understanding of hardware architecture. HLS abstracts away many of these complexities, allowing designers to express their ideas and algorithms in familiar software programming languages.

At its core, HLS involves three main steps:

- High-Level Design Entry: Designers create or adapt algorithms in programming languages like C or C++.

- Behavioral Synthesis: The HLS tool automatically generates an abstract hardware model from the programmed code, capturing the intended behavior.

- RTL (Register Transfer Level) Synthesis: The abstract model is further transformed into RTL code, which represents the actual digital hardware primitives and their interconnections.

The Significance of HLS

High-Level Synthesis has brought about a paradigm shift in digital hardware design by offering several significant advantages:

- Productivity Boost: By allowing designers to work at a higher level of abstraction, HLS dramatically reduces the time required for hardware development. It empowers software engineers to contribute to hardware design, leveraging their existing programming skills.

- Rapid Iteration: The software-like development flow of HLS enables rapid prototyping and iteration, enabling designers to experiment with different algorithms and architectures more efficiently.

- Hardware Optimization: HLS tools incorporate advanced optimization techniques, ensuring that the generated hardware is both high-performing and energy-efficient. Designers can focus on functionality, while the tool takes care of architecture-specific optimizations.

- Reduced Learning Curve: Traditional hardware design often required a steep learning curve for software engineers transitioning to hardware. HLS eliminates this barrier, enabling a broader pool of developers to engage in hardware design.

- Design Space Exploration: HLS tools provide insights into different design options and trade-offs, allowing designers to explore various implementations and select the one that best fits their requirements.

HLS Challenges and Considerations

While High-Level Synthesis offers compelling advantages, it’s not without challenges:

- Abstraction Limits: Not all algorithms or designs are easily expressible in programming languages. Some designs may require intricate low-level control that HLS cannot easily capture, such as dynamic memory allocation.

- Verification and Debugging: As designs become more complex, ensuring their correctness and debugging potential issues can be challenging. Traditional hardware design methodologies often provide more comprehensive debugging tools.

- Tool Maturity: The effectiveness of HLS tools varies, and not all designs can be efficiently synthesized. Some tools may struggle with certain types of algorithms or generate suboptimal hardware.

- Code Optimization: While HLS tools offer optimization capabilities, achieving the highest performance and efficiency may still require manual intervention and expertise.

Most importantly, you need to understand hardware architecture and have a solid understanding how your code will end up on the FPGA or SoC in order to properly use the tool. If you don’t understand these things, you may run into timing challenges and resource problems if the code is not written in a way that is hardware friendly. The tools do optimize your code to an extent, but there are limitations.

Understanding High-Level Synthesis in Vitis

Vitis, developed by Xilinx and now part of AMD, is a unified software platform designed to accelerate the development of applications targeting Xilinx FPGAs and adaptive SoCs (System on Chips). The Vitis HLS tool is available within the Unified IDE. HLS allows developers to express their algorithms and applications using familiar programming languages such as C, C++, and SystemC, making FPGA development more accessible to software engineers.

Here’s how the process works:

- High-Level Design Entry: Developers write their algorithms or applications using C, C++, or SystemC, abstracting away the low-level hardware details.

- HLS Transformation: The Vitis HLS tool takes this high-level code and generates hardware descriptions in RTL (Register Transfer Level) code, like VHDL or Verilog. This abstracts the process of hardware generation and optimization from the developer.

- Integration with Vitis Unified Software Platform: The generated RTL code can be seamlessly integrated into the Vitis Unified Software Platform, where developers can create hardware-software co-designs for their FPGA-based applications.

HLS and Vivado

From AMD:

“Vitis HLS is tightly integrated with both the Vivado Design Suite for synthesis, place, and route, and the Vitis core development kit for heterogeneous system-level design and application acceleration.

Vitis HLS can be used to develop and export:

- Vivado IP to be integrated into hardware designs using the Vivado Design Suite

- Vitis kernels for use in the Vitis application acceleration development flow”

The Benefits of HLS in Vitis

High-Level Synthesis within the Vitis platform brings a plethora of advantages to FPGA design:

- Faster Development: Developers can focus on algorithm design and functionality, significantly reducing the time required to create FPGA-accelerated applications. This is especially beneficial for applications that need to be developed and deployed quickly.

- Software-Hardware Co-Design: Vitis HLS enables the creation of hybrid designs that combine software running on processors with custom hardware accelerators. This synergy enhances the overall performance of applications by leveraging the strengths of both software and hardware.

- Code Reusability: Developers can reuse their existing software codebase, reducing the need for learning new hardware description languages. This also streamlines the transition for software engineers venturing into FPGA development.

- Optimization: The Vitis HLS tool performs automatic optimizations on the generated hardware, ensuring that the resulting design is efficient in terms of performance, resource utilization, and power consumption.

- Rapid Iteration: HLS allows for rapid prototyping and iteration, enabling developers to experiment with different algorithms and hardware architectures without the need for manual RTL coding.

Challenges and Considerations with Vitis

While High-Level Synthesis within the Vitis platform offers remarkable advantages, there are a few considerations:

- Algorithm Suitability: Not all algorithms are suitable for HLS. Complex control structures, memory management, and fine-grained optimizations might be better addressed through traditional RTL design.

- Performance vs. Flexibility: While HLS optimizes designs for performance, certain applications requiring extensive fine-tuning or hardware-specific optimizations might still benefit from traditional RTL design approaches.

Looking Ahead with Vitis

As FPGA technology continues to advance, the role of High-Level Synthesis will definitely grow. The integration of HLS into the unified software platform demonstrates commitment of AMD (Xilinx) to making FPGA development more accessible and efficient. The ongoing improvements in HLS tools and methodologies will further empower developers to harness the full potential of FPGA acceleration for a wide range of applications, from AI and machine learning to high-performance computing and beyond.

Does Intel have HLS?

Quartus Prime, developed by Intel, is a comprehensive software suite designed for FPGA design and development. Intel offers the Intel HLS Compiler in the Intel Quartus Prime Design Software Pro Edition installation. The original intent of this Intel HLS tool was for data center applications. While the AMD Vitis tool is the industry standard, the use of the Intel HLS Compiler is growing.

Conclusion

High-Level Synthesis represents a transformative approach to digital hardware design, offering a bridge between the worlds of software and hardware. By enabling designers to work at higher levels of abstraction and automating the transformation from software-like descriptions to hardware implementations, HLS accelerates the design process, increases productivity, and unlocks new opportunities for innovation in the field of electronics and digital design. As technology continues to evolve, HLS will remain a critical tool in shaping the future of hardware development.

For more information:

Courses:

Check out our on-demand webinar HLS: What Is It and When Do You Use It? here

OR

Check out our class, High Level Synthesis with the Vitis HLS Tool.

Design:

If you’re looking for design expertise to get your HLS designs completed and verified faster, reach out to us.

Guides:

Intel High Level Synthesis Compiler Pro Edition: Getting Started Guide