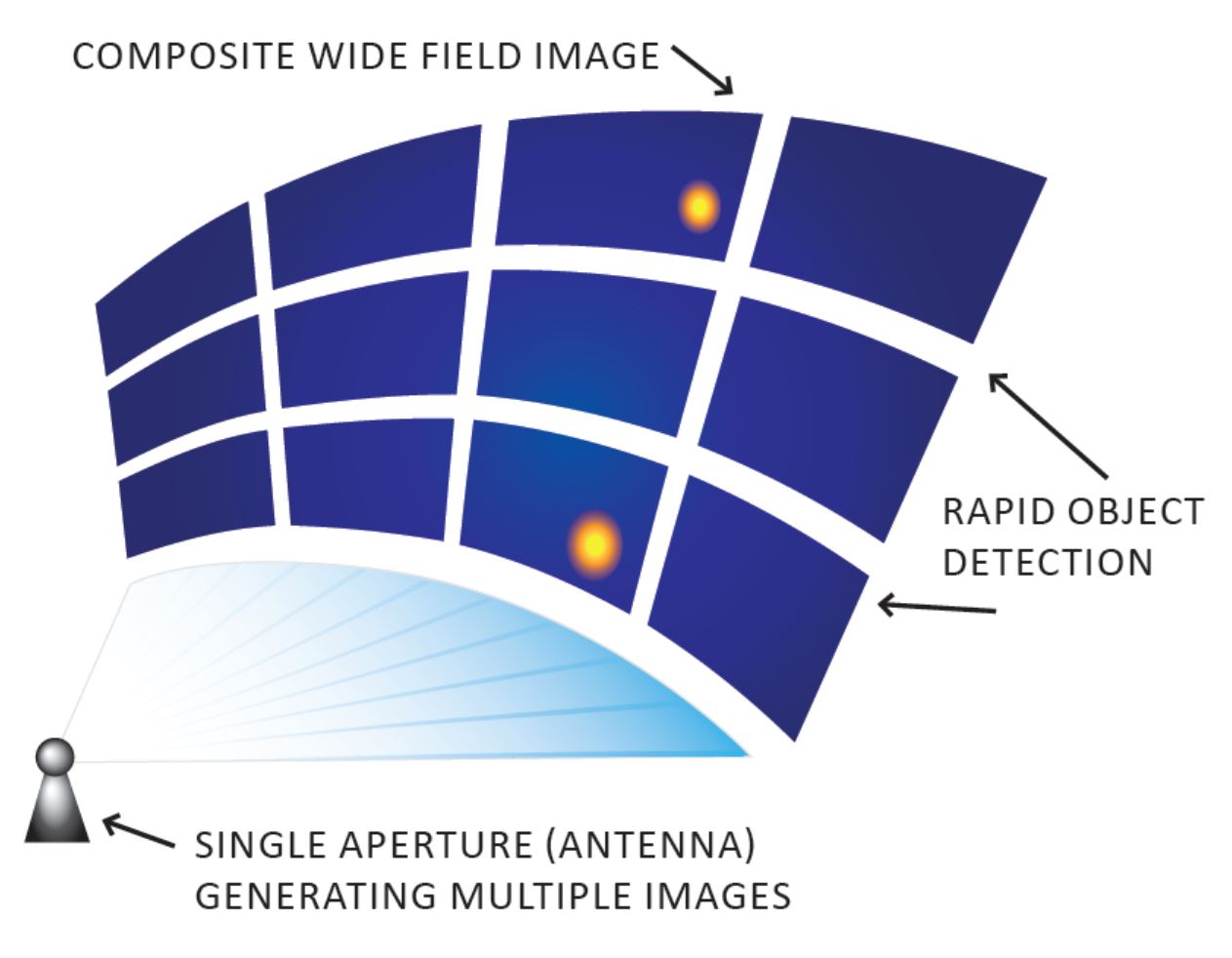

Synthetic Aperture Radar (SAR) works by moving the Aperture (antenna) through space and compiling a result based on a compilation of the varying views of the data captured. As such, SAR processing involves demanding, high-throughput computations, especially when resolution, latency, and scalability are critical. To demonstrate what’s possible with the AMD Versal Adaptive SoC, AMD engaged BLT to develop a reference design that highlights the capabilities of the Versal AI Engine architecture in a real-time radar imaging application.

This post outlines BLT’s design, its implementation on the Versal VCK190 evaluation board, and the performance characteristics achieved through AI Engine acceleration.

SAR Design Objectives

The goal was to use the AMD AI Engines to perform this challenging task; One that AI Engines excel at thus freeing up precious fabric, reducing overall power consumption and easing timing closure.

Our design is capable of:

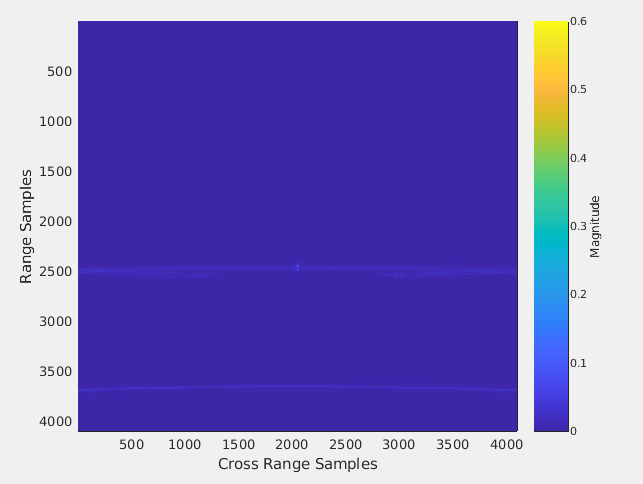

- Real-time 4K × 4K image processing

- High frame rate operation

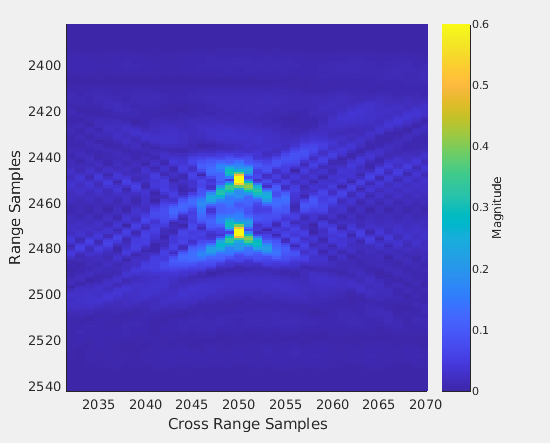

- Instant object detection

- Low latency

- Support for multi-antenna systems

- Efficient use of silicon resources

- Configurability for power-constrained platforms

Traditional fabric-only designs can meet SAR performance requirements, but often at the cost of complexity, high resource usage, and limited headroom for other functionality. The Versal AI Engine array provides an alternative: vectorized, parallel compute cores with tight interconnect and low latency, well-suited to the signal processing used in SAR systems.

Architecture Overview

BLT implemented this SAR processing design using the AI Engine array on the AMD Versal VCK190. Key operations were mapped to AI Engine tiles to take advantage of VLIW parallelism and deterministic dataflow.

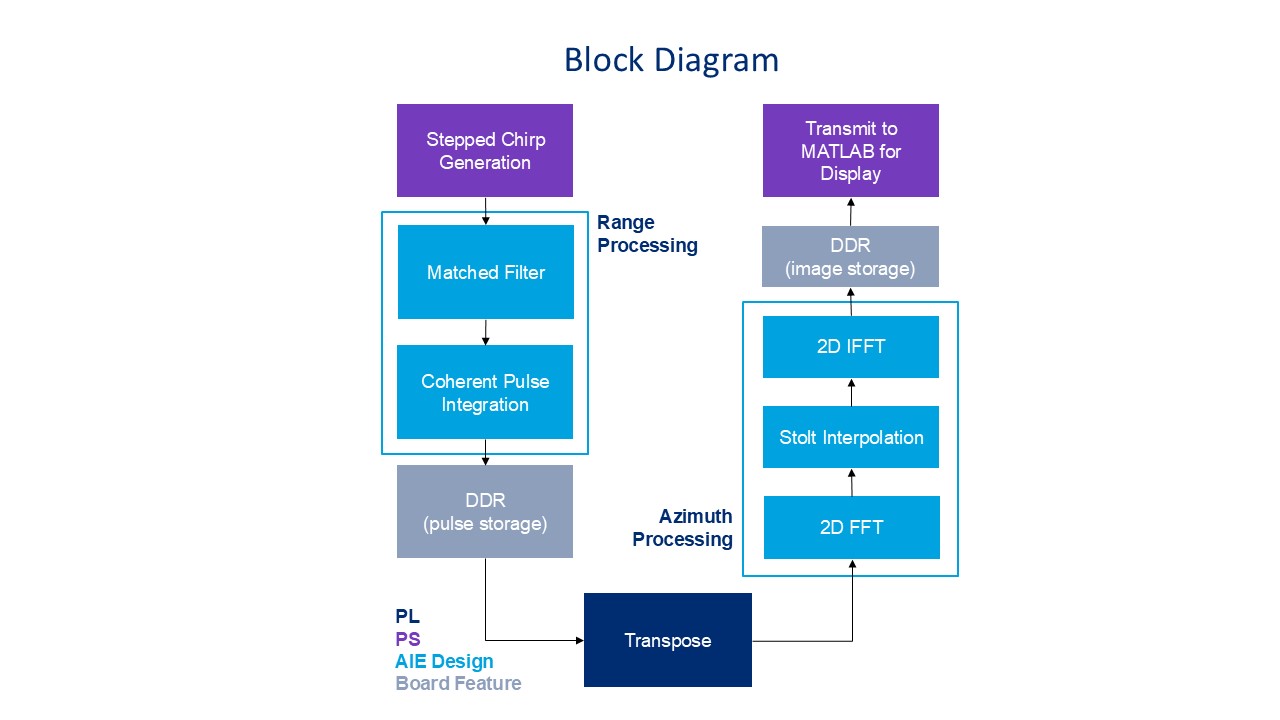

Block Diagram:

All major computations were assigned to the AI Engine array, while the programmable logic and processing system handled control, interfacing, and memory management. This partitioning left significant fabric capacity available for expansion.

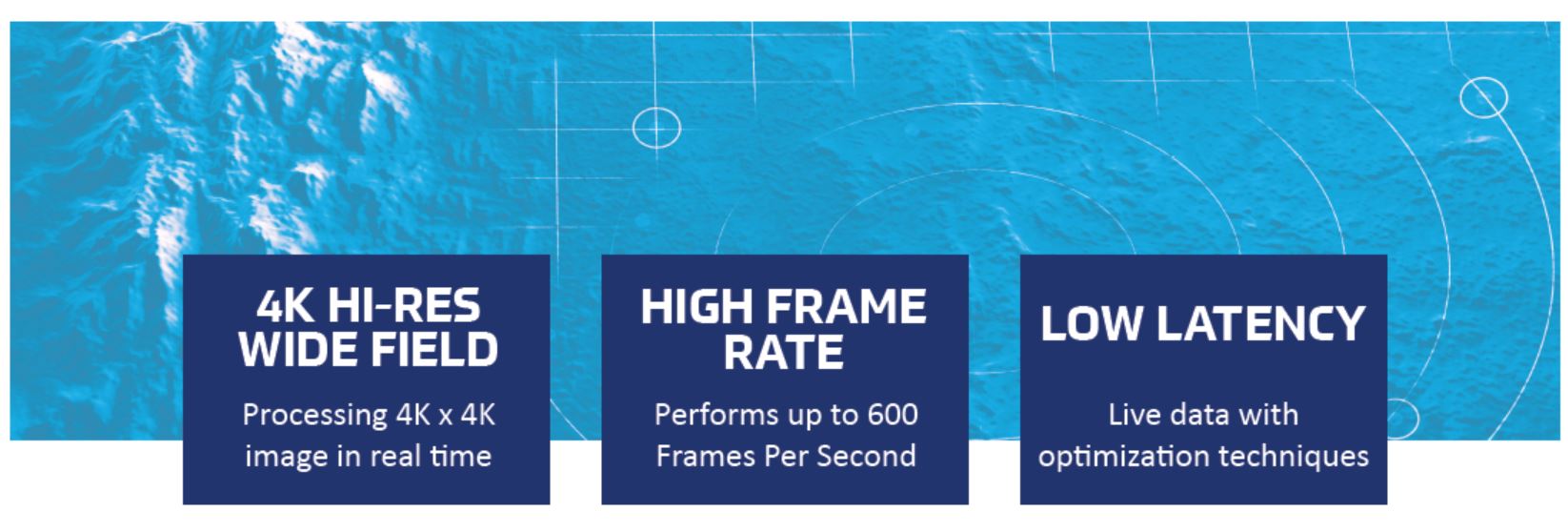

Performance Summary

This design is capable of processing an exceptionally high number of megapixels (MP) per second, making it optimal for high-throughput imaging applications. Our design utilizes the AMD Versal VCK190, which has 400 AI Engine cores, ideal for processing hi-res object detection SAR. 0.7MP / Core

- 70MP / Core / Second

- Up to 600 FPS (frames per second)

- 4K x 4K hi-res image

- Live data (low latency), approx. 20ms

- Suitable for multiple antennas

The result is a highly efficient SAR engine with performance suitable for airborne, space-based, or ground radar systems, especially in scenarios where SWaP constraints are non-negotiable.

Thanks to the high frame rate, the module can also sweep multiple 4K x 4K spatial regions and still deliver effective real-time performance.

Engineering Approach

This design required careful workload partitioning, memory management, and streaming architecture to keep data movement tightly coupled with computation. BLT’s experts worked at the lowest levels to maximize performance and take full advantage of:

- AI Engine vector and scalar units

- Stream and cascade interfaces between tiles

- Low-latency tile-to-tile communication

- Parallel instruction-level and data-level execution

Our engineering team modeled the full pipeline to ensure predictable throughput and scaling behavior. Optimization focused on minimizing stall conditions, balancing tile workloads, and integrating host and memory management across the PL and PS domains.

About the Team

BLT has been developing signal processing systems using AMD (formerly Xilinx) silicon for over 35 years. We work at every level of the stack: algorithm, architecture, HDL, AI Engine programming, embedded software, and system integration. Our expert engineers have been working with Versal since its early release both for AMD and for major US defense contractors.

AMD selected BLT for this SAR reference design based on our deep experience with adaptive SoC architectures and a long history of delivering complex systems that meet performance, power, and schedule constraints.

Demoing This SAR Design

BLT has given talks and demoed this design at two separate technical events:

AMD Digital Signal Working Group, presented during the AMD Partner Night. BLT is an AMD Premier Partner.

AOC July Event at Johns Hopkins University Applied Physics Laboratory. BLT is an AOC Corporate Member and sponsor.

Conclusion

This SAR implementation illustrates how AI Engines on Versal devices can accelerate demanding radar workloads while preserving silicon for other tasks. The architecture supports high data rates, low latency, and flexible scaling, all within a compact, power-aware platform.

For teams evaluating Versal adaptive SoCs for radar, imaging, or other signal processing applications, this design provides a useful reference point for system partitioning, performance modeling, and AI Engine integration.

To learn more about this effort, contact us.