Vivado Intelligent Design Runs (IDR) are a powerful feature that helps designers achieve timing closure more efficiently. Timing closure is often one of the most persistent and frustrating challenges in FPGA development. For complex designs, especially those targeting UltraScale and UltraScale+ devices, traditional trial-and-error tuning of implementation strategies can lead to long debug cycles and inconsistent results.

What is IDR (Intelligent Design Runs)?

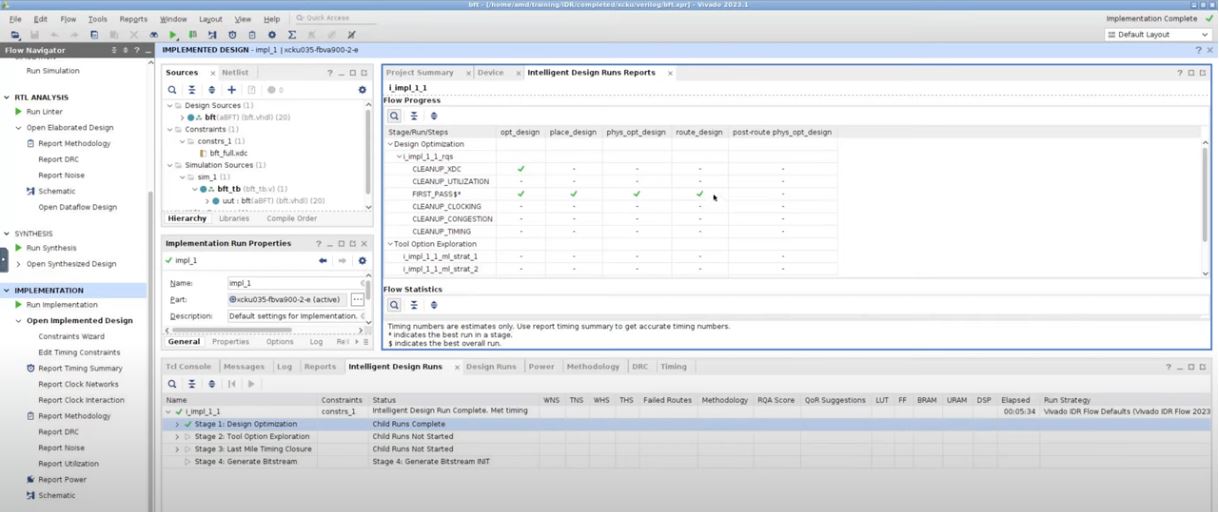

Vivado Intelligent Design Runs are an automation layer built into Vivado that streamlines the process of meeting timing. Rather than relying on a single implementation pass or manually trying various strategies, IDR intelligently explores multiple approaches across several stages. Each stage builds incrementally on the results of the previous one, progressively refining the implementation to improve performance.

IDR is available for AMD UltraScale and UltraScale+ devices. It is not supported on 7 Series parts. Vivado 2024.2 and above supports Advanced Flow for Versal Adaptive SoC devices instead.

When Should You Use Intelligent Design Runs?

IDR isn’t intended to replace a disciplined implementation flow. It’s a tool to use when you’ve already tried standard methods and still can’t meet timing. The recommended approach is to:

- Complete synthesis and implementation using your default strategy.

- Review timing reports and design rule checks (DRCs).

- If timing closure fails and manual intervention isn’t yielding results, use IDR to explore more complex, tool-driven options.

Running IDR too early, before you understand where your design stands, can lead to confusion and unnecessary tool cycles. It’s best used after you’ve baselined your design.

How Does It Work?

IDR operates in multiple stages. In each stage, Vivado applies different implementation strategies, analyzes results, and then intelligently chooses the most promising candidates to pass to the next stage. These stages include strategies like:

- Performance_Explore

- Performance_Retiming

- ExtraNetDelay_high

- And others, depending on the design’s needs

The strategy selection is guided by Vivado’s internal machine learning models, which evaluate prior results to choose strategies that are more likely to succeed in subsequent runs.

The runs themselves are incremental, building on each other using post-synthesis, post-place, and post-route results.

Support for HLS and HDL

Whether your IP is written in traditional HDL or generated using HLS (High-Level Synthesis), IDR will optimize it the same way. Once the HLS-generated IP is synthesized and integrated into the Vivado project, it’s treated just like HDL logic during implementation.

Tips for Using IDR Effectively

- Clock Relationships Matter: Vivado assumes clocks are related unless told otherwise. Use false path or asynchronous clock group constraints where necessary to get accurate timing analysis.

- Device Selection: IDR is only available for UltraScale or newer devices. If you don’t see the option in your Vivado project, make sure your part selection supports it.

- Script It If Needed: Like most Vivado features, IDR can be scripted using Tcl. The journal file logs all commands, so you can extract them to automate your flow.

Watch Our On-Demand Webinar on IDR (Intelligent Design Runs)

Looking to extend the performance of your design? Struggling to close timing? In this one-hour webinar, you’ll learn what the Intelligent Design Flow is, how to create an Intelligent Design Run, explore comprehensive reports and log files for an IDR, and execute a single pass run.

This webinar is a live demonstration and Q&A.

What About Version Upgrades?

One common question is whether IDR results are reusable across Vivado versions. The short answer is: not reliably. IP updates or tool changes can affect how your design implements, so when migrating to a newer AMD Vivado version, it’s typically best to rerun IDR to ensure you’re taking advantage of new optimizations and tool behavior.

Documentation and References

For a deeper dive, consult the Vivado Design Suite User Guide: Design Analysis and Closure Techniques (UG906). It includes detailed guidance on how to interpret timing reports and structure your implementation strategy.

Conclusion

Intelligent Design Runs aren’t a silver bullet, but they are an extremely useful tool for complex designs struggling to meet timing. By automating the exploration of multiple implementation strategies, IDR reduces manual guesswork and increases the likelihood of successful timing closure, especially when traditional methods have hit a wall.

If you’re developing for UltraScale or UltraScale+ platforms and looking to streamline your path to timing closure, Vivado’s IDR feature is worth integrating into your flow.