As FPGA designs grow in complexity, understanding how device resources are being used becomes increasingly important. Even designs that meet timing can run into issues if resources are overutilized or unevenly distributed. The Vivado Utilization Report in the AMD Vivado Design Suite provides a detailed breakdown of how the design maps onto the target device. It gives engineers visibility into resource consumption and helps guide decisions related to architecture, optimization, and device selection.

What the Vivado Utilization Report Shows

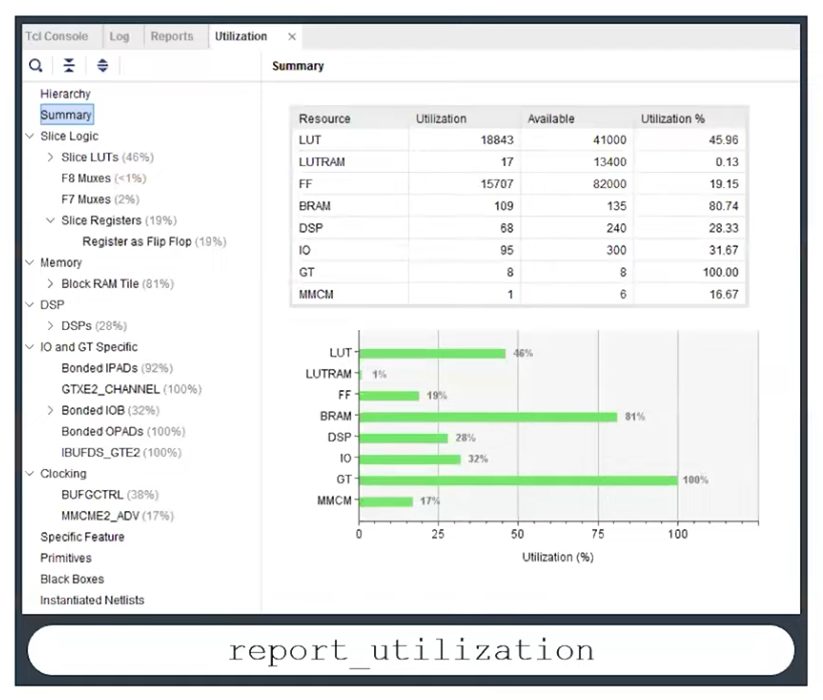

The Utilization Report summarizes how much of the FPGA’s available resources are used by the current design.

This includes:

- Lookup Tables (LUTs)

- Flip-flops (registers)

- Block RAM (BRAM)

- DSP slices

- Clocking resources

- IO Pins

- Transceivers

The report can be viewed at multiple levels, including:

- Overall device utilization

- Hierarchical utilization by module

- Distribution across resource types

Vivado also provides graphical views, such as histograms, to help visualize how resources are consumed.

Learn more about this AMD report.

Why Utilization Matters

Resource usage directly affects both performance and feasibility.

High utilization can lead to:

- Increased routing congestion

- Longer routing delays

- Difficulty achieving timing closure

Even if total utilization is within device limits, uneven distribution of logic can create localized congestion that impacts routing efficiency. Conversely, very low utilization may indicate room for additional functionality or an opportunity to optimize device selection.

Identifying Problem Areas

The hierarchical view of the Utilization Report is especially useful for identifying which parts of the design consume the most resources.

This allows engineers to:

- Locate modules with excessive LUT or register usage

- Identify inefficient implementations

- Determine whether specific blocks should be optimized or restructured

For example, a single module consuming a large percentage of available LUTs may benefit from pipelining, resource sharing, or algorithmic changes.

Correlation with Timing and Routing

Utilization is closely tied to timing performance.

Designs with high resource usage often experience:

- Increased routing complexity

- Longer critical paths

- Greater difficulty meeting timing constraints

In these cases, reviewing utilization alongside timing reports can help identify whether performance issues are related to logic density or placement challenges.

Learn more about timing reports here.

Using Utilization During Design Iteration

The Vivado Utilization Report is most effective when used iteratively throughout the design process. After synthesis, it provides an early estimate of resource usage. After implementation, it reflects actual placement and can reveal how resources are distributed across the device. By comparing utilization across iterations, engineers can track the impact of design changes and ensure that optimizations are moving in the right direction.

Practical Considerations with the Vivado Utilization Report

When reviewing utilization, it is helpful to:

- Compare usage against device capacity

- Look for imbalances between resource types

- Review hierarchical breakdowns for hotspots

- Consider how utilization may affect routing and timing

This context helps determine whether a design is well-balanced or likely to encounter issues during implementation.

Vivado Utilization Report Conclusion

The Vivado Utilization Report provides essential insight into how a design maps onto FPGA resources. By understanding both overall usage and hierarchical distribution, engineers can identify inefficiencies, anticipate routing challenges, and make informed design decisions. Used alongside timing and routing analysis, it plays a key role in achieving a design that is both efficient and scalable.