Managing clock domain crossing (CDC) is one of the most critical — and sometimes confusing — challenges in FPGA design. With modern designs often spanning multiple clock domains, ensuring safe data transfer across these domains is essential to avoiding metastability, timing issues, and unreliable system behavior.

In this post, we’ll walk through how to approach CDC challenges using AMD Vivado’s built-in tools, how to properly implement synchronization circuits, and best practices to verify your design’s robustness.

What is Clock Domain Crossing (CDC)?

Clock Domain Crossing (CDC) refers to the process that occurs when signals are transferred between two different clock domains in a digital system. These clock domains may have distinct clock sources or different frequencies, which can introduce challenges in maintaining the integrity of data. Essentially, CDC happens when data is transmitted from one part of a design operating under one clock to another part that runs on a different clock, potentially with an unknown phase relationship.

In FPGA and ASIC designs, this is a crucial concept because improper handling of CDC can lead to metastability, data corruption, or even timing violations, which can affect the overall system’s reliability. These issues arise when the receiving flip-flop or register does not reliably capture the input signal due to the asynchronous nature of the clocks involved.

Handling CDC correctly is essential to avoid:

- Metastability: A condition where a flip-flop or register does not settle to a stable logic level in time, leading to unpredictable behavior.

- Data Corruption: When data is incorrectly captured due to timing mismatches between clocks.

- Timing Violations: When setup and hold times are not met due to asynchronous clock domains, causing the design to fail timing constraints.

In Vivado, tools and strategies are available to analyze, detect, and correct CDC issues, such as the use of synchronizers or cross-domain FIFOs, which are specifically designed to manage data transfer between clock domains safely.

How and When to Use Clock Domain Crossings

Clock Domain Crossing (CDC) is a critical consideration when designing systems that involve multiple clock domains, such as in complex FPGA or ASIC designs. Properly implementing CDC ensures reliable data transfer between different clock regions.

How to Use CDC

There are several techniques available for implementing CDC in your design. The approach you choose depends on the complexity of your design, the number of clock domains, and the type of data being transferred. Below are common methods for handling CDC:

- Synchronizers: Use two flip-flops in series to transfer a signal between clock domains safely.

- FIFO Buffers: Employ FIFOs for multi-bit data transfers, ensuring safe storage and retrieval between clock domains.

- XPM Blocks: Leverage Xilinx’s CDC IP blocks for simplified synchronization, especially for bus signals.

- Clock Buffers/Interconnects: Use these for managing complex interactions between multiple clock domains.

- Vivado CDC Tool: Run CDC reports in Vivado to automatically detect and analyze potential CDC issues in your design.

When to Use CDC

CDC should be considered and implemented under the following circumstances:

- Multiple Clock Domains: When your design has more than one clock source, especially with different frequencies or phases.

- Signal Transfer Across Domains: If you need to pass signals between clock domains, CDC is necessary to ensure data integrity.

- Asynchronous Signals: When clocks are asynchronous and there’s no predictable phase relationship between them.

- High-Speed Designs: In systems with high-speed data transfers, CDC prevents errors due to timing mismatches.

- Debugging Complex Systems: For debugging designs with multiple clock domains, proper synchronization ensures reliable analysis with tools like ILAs.

By properly identifying when and how to apply CDC methods, you can ensure that your design remains stable, reliable, and free from synchronization issues, even in the most complex systems with multiple clock domains.

Understanding and Identifying Clock Domain Crossing Risk

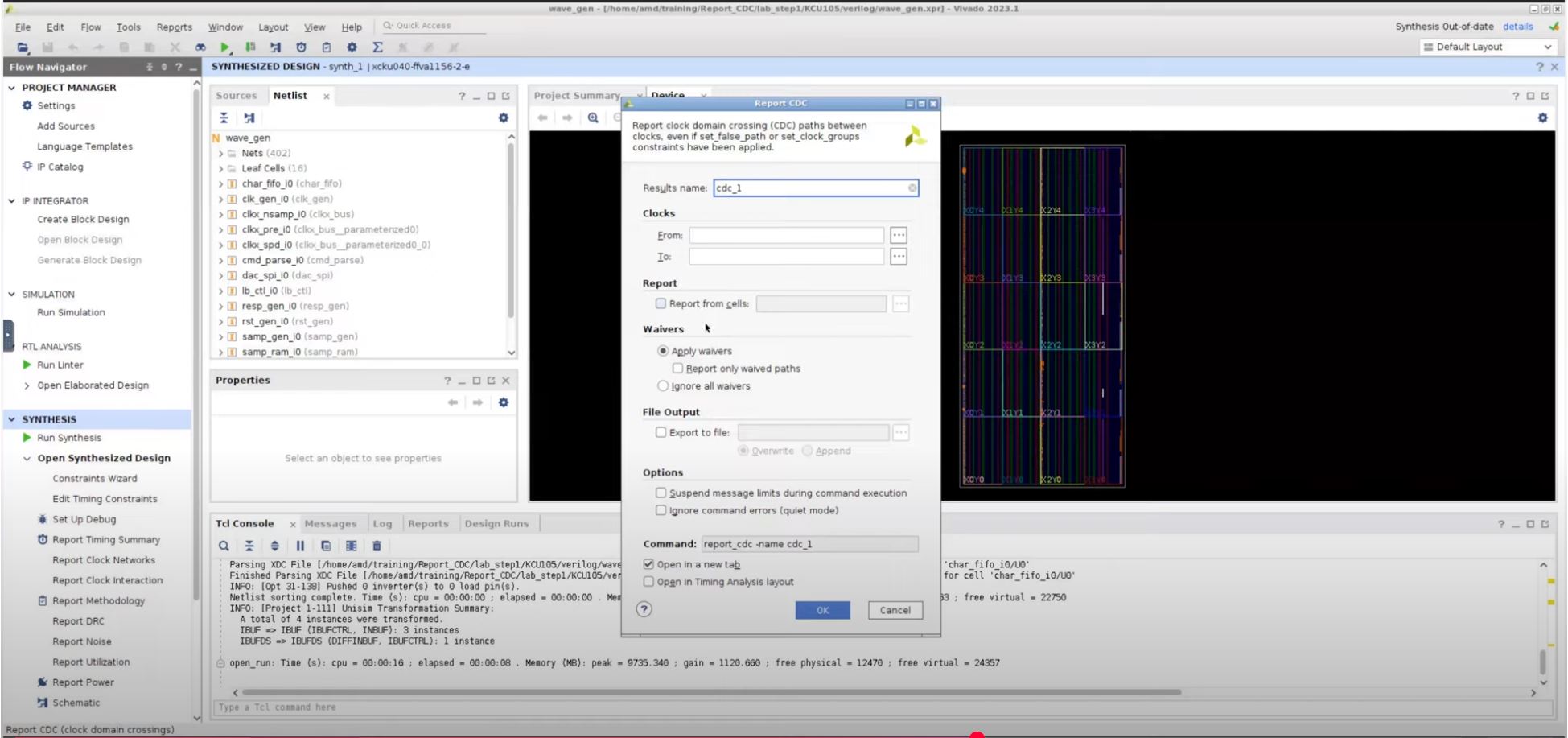

After running synthesis, your first step should be to review the Report CDCs under “Reports → Timing” in Vivado.

This report highlights potential unsafe crossings where signals move from one clock domain to another.

In many cases, you’ll see warnings for signals that have not been properly synchronized. Some common early indicators include:

- Missing or incorrect synchronization structures.

- Single-bit signals crossing domains without explicit handling.

- Multi-bit signals crossing domains without proper data stability guarantees.

The CDC report, paired with Vivado’s schematic and hierarchy viewers, makes it easier to zero in on these problematic areas.

Building Proper Synchronization Circuits

Synchronization circuits are crucial when a signal transitions between asynchronous clock domains. Typically, this involves using a small register chain, usually two or more flip-flops, to reduce metastability risk.

In Vivado, you can identify synchronization chains by looking for registers that serve as the first and second stages of the synchronizer.

ASYNC_REG attributes are often added to these synchronization registers to help the tool recognize and correctly optimize them.

You can set the ASYNC_REG property manually in RTL:

verilog

(* ASYNC_REG = "TRUE" *) reg signal_meta;

(* ASYNC_REG = "TRUE" *) reg signal_dest;

Or you can apply it using a constraint:

tcl

set_property ASYNC_REG true [get_cells -hierarchical *meta_reg*]

Note: Always validate constraints carefully. Wildcard matches can unintentionally apply properties to unrelated cells.

Watch Our On-Demand Webinar on Clock Domain Crossing

This one-hour webinar will discuss all of the basics of what clock domain crossings (CDCs) are and how you can navigate them safely. We will discuss how to do single bit CDCs, several methods for CDC busses, and also the Xilinx Parameterized Macros (XPM) for CDC.

This webinar is a live demonstration and Q&A.

Verifying Synchronization After Implementation

After implementation:

- Rerun Report CDCs to confirm that synchronization issues are resolved.

- Use Vivado’s Schematic and Device View to inspect placement.

- Verify that the flip-flops in a synchronization chain are tightly packed, ideally into the same slice, minimizing setup and hold timing risks.

Additionally, Vivado offers the Report Synchronizer MTBF tool. This report estimates the Mean Time Between Failure (MTBF) for synchronizers, giving you a quantitative check on your system’s metastability resistance.

CDC Solutions for AXI Interfaces

Handling CDC for AXI interfaces requires special attention, particularly in larger systems with multiple bus masters and slaves.

Vivado provides specialized IP for this purpose:

- AXI Stream CDC IP: Manages clock domain crossings for AXI-Stream interfaces.

- AXI Clock Converter IP: Used for memory-mapped AXI transactions across different clock domains.

- AXI Interconnect: Incorporates clock domain crossing logic automatically for more complex bus architectures.

When working with AXI, using these dedicated IP blocks ensures protocol integrity without needing to manually build CDC handling logic.

Debugging Across Clock Domains

When using Integrated Logic Analyzers (ILAs) for debug:

- Always ensure that the ILA’s clock matches the domain of the signals it captures.

- If your design includes multiple clock domains, instantiate separate ILAs per domain.

- To correlate events across domains during debug, align your capture windows carefully.

This approach avoids CDC-related capture issues and ensures accurate visibility into your system’s behavior.

Conclusion

Clock domain crossing isn’t just a checkbox, it’s a critical foundation for reliable FPGA designs. By using Vivado’s CDC reports, building proper synchronization circuits, applying async_reg attributes where appropriate, and leveraging AXI-ready IP for complex systems, you can confidently handle even the most demanding multi-clock designs.

Mastering CDCs today ensures your systems are robust, scalable, and ready for future growth.