The AXI protocol is powerful and easy-to-use for connecting modules within SoCs and FPGAs.

Intro to the AXI Protocol

AXI (Advanced eXtensible Interface) is an interface for connecting modules within an SoC or an FPGA. It is fully synchronous and can be as wide and as fast as needed to meet transfer requirements between modules. The strength of AXI is that it provides a robust means to control and verify that data has transferred, either single-strobe, burst, or streaming, while being easy to understand and implement.

AXI, more formally known as AXI4, is part of the Advanced Microcontroller Bus Architecture (AMBA) developed by ARM, also known as the “Digital Highway from ARM”. AMBA also includes the Advanced Peripheral Bus (APB) and the Advanced High-Performance Bus (AHB) bus interface protocols. Together, they provide the protocols needed to implement an interconnected SoC containing a complex mixture of heterogenous processors and peripherals.

AXI and FPGAs

Within an FPGA, AXI4 is typically used to transfer data to and from memories using a memory-mapped architecture or from module to module using a streaming protocol without addressing. There are two types of AXI4 used for memory-mapped transfers. AXI4-Full supports burst memory-mapped transfers such as used with DDR memories. These can be either reads or writes and they can be re-ordered by modules to maximize throughput. AXI4-Lite also supports memory-mapped reads and writes but it does not support bursts. It is normally used as a control interface to a peripheral that accesses control and status registers. AXI4-Stream is a unidirectional interconnect protocol that can either support single-strobe transfers, bursts, or continuously streaming data transfer. Its data is never re-ordered.

AXI is not a chip-to-chip interface. Its definition makes it very useful for module-to-module interconnect within an FPGA or SoC. There are memory-mapped and streaming chip-to-chip interfaces that better manage the challenges of voltage levels and terminations and clock propagation, like SPI, Ethernet, DDR or PCIe. Additionally, most chip-to-chip interfaces are supported by IP modules within the FPGA or SoC that then have AXI ports for transferring the data to internal IP blocks.

Learn more about what AXI is in this blog post.

AXI Protocol Benefits

The primary benefits of using modules with AXI connectivity are its availability, productivity and flexibility.

Availability

Many FPGAs are supported by an extensive library of IP blocks that can be interconnected using AXI. Often times these IP blocks are provided at no-cost when implemented within FPGAs and SoCs. Additionally, many other IP vendors provide modules that can be licensed and then easily implemented and interconnected using AXI ports. There are over 400 ARM partners offering IPs and tools that support the AXI interconnect ecosystem.

Productivity

Use of the AXI interconnect protocol provides a single interconnect standard across ALL domains and ALL partner IPs. Therefore, there is only one standard to learn to perform these various interconnects. This increases productivity as time is not spent in design, implementation and simulation to create and verify dissimilar interconnect protocols. Significant time is often expended while validating, and iteratively fixing, modules with dissimilar interconnect protocols. Therefore, using the AXI interconnect protocol results in less time spent interconnecting IPs into a design and then validating robust operation.

Flexibility

Since the AXI interconnect protocol is not limited in speed or width, it provides the ability to configure the interconnect to meet and balance the system goals of performance, area, and power. Also, having a consistent interconnect protocol by using AXI enables a seamless FPGA design.

Since AXI-Full and AXI-Lite are commonly used for accessing memory-mapped memories and peripherals, the data widths are normally implemented as a multiple of 8 to support byte-wide data. Bit widths of 32, 64, 128, or even 512 bits are common. The AXI-Stream interface supports streaming data with a width of any number of bits and therefore is commonly used for DSP, video, and communication applications.

AXI Quality of Service (QoS)

AXI Quality of Service (QoS) is a feature that enables system designers to prioritize and manage data traffic within an SoC or FPGA. QoS settings in AXI interfaces allow different transactions to be assigned priority levels, ensuring that critical data transfers receive preferential treatment over lower-priority traffic. This is particularly useful in systems where multiple masters compete for access to shared resources, such as memory controllers or high-speed peripherals. By implementing QoS, designers can optimize bandwidth allocation, reduce latency for time-sensitive operations, and prevent resource starvation in complex designs. AXI QoS signals, provide a mechanism for masters to indicate the priority of write and read transactions, respectively, allowing arbitration logic to make informed scheduling decisions. Proper utilization of QoS settings enhances system performance, improves real-time processing capabilities, and ensures smooth operation in applications like video processing, networking, and high-performance computing.

AXI Applications

As discussed previously, AXI interfaces are point-to-point interconnects. There is a master side of the interconnect which is the side that initiates the transactions. Then there is a slave side of the interconnect which is the responder. The slave side can never initiate a transfer. It can send data to the master but only when the master side requests it first. You may think that this interface description would severely limit its usefulness. However, you need to separate the functionality of the IP block from its interfaces. AXI provides the interfaces to the modules but does not restrict the functionality of the IP module.

AXI BRAM Controller

Let’s consider an AXI BRAM Controller. This IP module has up to 2 AXI4 memory-mapped ports, and when paired with a BRAM block, it provides a dual-port memory. The AXI ports are slave ports that can connect to master ports from different initiators. The AXI BRAM Controller IP manages the slave ports and their connections to the BRAM block. As you can see, the point-to-point nature of the AXI interfaces does not prevent the AXI BRAM Controller from connecting multiple AXI4 masters to a single slave memory block.

AXI SmartConnect

A more complex AXI IP module is the AXI SmartConnect. The AXI SmartConnect IP module can be used to connect one or more master interfaces to one or more slave interfaces. For instance, you could have a processor master and a DMA controller master both connected to several slave peripherals. Additionally, these masters and slaves could be in different clock domains and have different byte widths. The AXI SmartConnect IP module will be implemented by the tools with the clock-domain-crossing bridges, arbiters, and buffers needed to transfer data between the AXI interface master and slave ports. The AXI ports are still connected point-to-point to each of the master modules and to each of the slave modules.

AXI Multi-Channel DMA Module

The previous two example modules with multiple AXI ports operated only with the AXI memory-mapped interface types. The AXI Multi-Channel DMA module is a Packet DMA module with scatter-gather capability that can have both master and slave AXI-Stream ports for packet data, separate AXI-Full master ports for scatter-gather look-up table and block memory storage in memories like DDR, and an AXI-Lite port for configuration and control. Each of these AXI ports are point-to-point interconnects whereas the AXI Multi-Channel DMA IP contains the logic and buffers needed to transfer packet data streaming through at the connected line rate.

These are just a few examples. FPGA vendors provide hundreds of IP modules containing AXI ports. Also, as stated, there are many solution providers that also produce IP modules that have AXI-compliant ports.

Be the first to know. Sign up for our newsletter.

AXI Protocol Functionality

Although AXI interfaces can often be comprised of over 100 pins, the implementation is modular, and each group of signals, or channels, operates in a similar way. AXI-Full and AXI-Lite interconnects have five separate unidirectional interconnect channels that operate independently. These are the Read Address, the Read Data, the Write Address, the Write Data, and the Write Response channels. Even though this may appear very complex, each uses a simple handshaking protocol to present and pass data robustly. AXI-Stream only has a single channel whereas the transfer protocol works the same way.

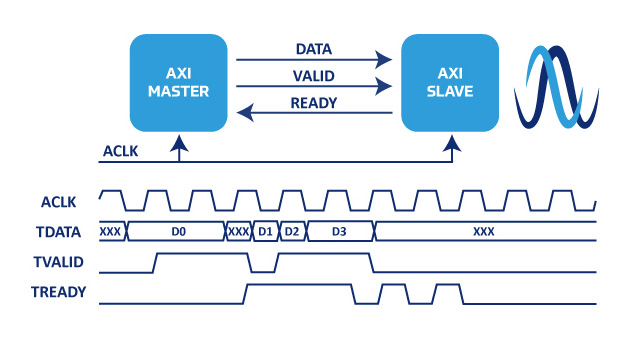

TVALID and TREADY

This explanation of a simple AXI-Stream interconnect highlights the handshake process used to pass data from module to module. The minimum list of signals required to comprise an AXI-Stream interconnect is ACLK (clock), TVALID (valid), TREADY (ready) and TDATA (data). The data bus can be of any arbitrary width. Each interconnect is point-to-point and unidirectional. A common clock is provided to both the data source (the master module) and the data destination (the slave module). The valid signal is output from the master module when it has data available to transfer. The ready signal is output from the slave module when it is able to receive data. Data transfer occurs when the valid signal and the ready signal are active high when sampled on the same rising-edge clock pulse.

Lets restate that in a step-by-step process along with a figure.

- The master asserts and holds TVALID active high when TDATA is available and ready for transfer.

- The slave asserts TREADY active high when able to receive TDATA.

- TDATA is deemed transferred when TVALID and TREADY are high (active) when sampled on the same rising ACLK edge (i.e. the slave will receive the TDATA on this clock edge).

- If the master has more TDATA available to send on the next ACLK rising edge, it presents the new TDATA on its output and continues to assert TVALID. Otherwise, it de-asserts TVALID to indicate that it does not have more TDATA ready to transfer.

- Similarly, if the slave is not ready to receive more TDATA, it will de-assert TREADY so that no further transfers occur until it is ready to receive more TDATA.

The figure below illustrates this process in operation as the AXI master port successfully transfers TDATA words D0, D1, D2, and D3 to the AXI slave port.

Conclusion

AXI is a fundamental and versatile interconnect protocol that simplifies the integration of IP modules within FPGAs and SoCs. Its structured approach to memory-mapped and streaming data transfers, combined with its robust handshaking mechanism, ensures reliable data exchange between components. The widespread adoption of AXI in FPGA and SoC designs, supported by extensive IP libraries and toolchains, makes it an essential technology for high-performance computing, embedded systems, and real-time applications. By leveraging AXI’s flexibility, engineers can efficiently build scalable, high-bandwidth architectures that meet the demanding requirements of modern digital systems.